硬件描述语言(VHDL)的教程VHDL教程提供了VHDL的基本和高级概念。我们的VHDL教程是为初学者和专业人士设计的。

什么是HDL?HDL代表硬件描述语言.这是一个编程语言那是用来描述、模拟、而且创建硬件,如数字电路(ICS)。HDL主要用于发现设计中的故障,然后在硬件上实现。 HDLs的主要优点是它提供了灵活的建模能力,并且可以表示大型复杂的设计(>107盖茨)。 今天,市场上有许多可用的hdl,但是硬件描述语言(VHDL)而且Verilog是最流行的hdl。 什么是VHDL?VHDL是Very High-Speed Integration Circuit HDL(硬件描述语言)的缩写。它是IEEE(电气和电子工程师协会)标准硬件描述语言,用于描述和模拟复杂数字电路的行为。 VHDL最流行的例子是奇偶校验发生器,脉冲发生器,优先编码器,行为模型16个字,8位内存等。 VHDL支持以下特性:

什么是Verilog?Verilog也是一种HDL(硬件描述语言),用于描述电子电路和系统。它用于硬件仿真和综合。 Verilog最流行的例子是网络交换机、微处理器、内存、简单触发器等。 VHDL和Verilog的区别

VHDL的历史VHDL由美国国防部(DOD)于1980年开发。

为什么硬件描述语言(VHDL) ?VHDL的用途如下:

VHDL的优点VHDL的优点如下:

VHDL的缺点VHDL的缺点如下:

VHDL的基本元素VHDL有以下三个基本元素: 1.实体实体用于指定电路的输入和输出端口。一个实体通常有一个或多个端口,可以是输入(in)、输出(out)、输入-输出(inout)或缓冲区。 一个实体还可以包括一组通用值,用于声明电路的属性。 实体声明 您可以使用以下语法声明一个实体:

例子:

如果一个实体是通用的,那么它必须在端口之前声明。泛型没有模式,所以它只能将信息传递到实体中。 语法: 例子: 端口名称书写规则: —端口名称由字母、数字和下划线组成。 港口方式 输入端口 2.体系结构架构是设计的实际描述,用于描述电路如何运行。它可以包含并发语句和顺序语句。 建筑宣言 架构可以使用以下语法声明: 例子: 3.配置配置定义了如何将设计层次结构链接在一起。它还用于将体系结构与实体相关联。 配置声明 例子: VHDL中建模样式的类型在VHDL中有4种类型的建模风格: 1.数据流建模(设计方程) 数据流建模可以基于布尔表达式进行描述。它显示了数据如何从输入流向输出。它工作于并发执行。 2.行为建模(解释行为) 行为建模用于按顺序执行语句。它显示了系统如何根据当前语句执行。 行为建模可能包含流程语句、顺序语句、信号分配语句和等待语句。 3.结构建模(子模块连接) 结构建模用于指定电路的功能和结构。 结构建模包含信号声明、组件实例和组件实例中的端口映射。 硬件描述语言(VHDL)对象VHDL使用以下三种类型的对象: 1.常量 常量是一个对象,它只能保存一个在整个代码中不能更改的值。 例子:常量number_of_bytes integer:=8; 2.变量 变量还保存给定类型的单个值。在模拟过程中,可以使用变量赋值算子来改变变量的值。 变量用在流程和子程序中。 变量由赋值操作符":="赋值。 例子: 变量索引:整数:=0; 3.信号 信号可以在体系结构中声明,并在体系结构中的任何地方使用。信号由赋值运算符赋值。< =". 例子: 信号sig1: std_logic; VHDL中的数据类型数据类型是存储数据的抽象表示。 在VHDL -中有以下数据类型 1.标量类型

2.复合类型

硬件描述语言(VHDL)操作符VHDL操作符用于构造表达式。 在VHDL中有以下类型的操作符: 1.逻辑运算符 逻辑运算符用于控制程序流。当逻辑运算符与信号或变量结合时,就用它来创建组合逻辑。 VHDL支持以下逻辑操作符:

2.关系运算符 在VHDL中,关系操作符用于比较相同数据类型的两个操作数,接收到的结果总是布尔类型。 VHDL支持以下关系操作符:

3.算术运算符 算术运算符用于进行算术运算。这些操作符是数值类型,例如整数而且真正的. VHDL使用以下算术运算符:

4.运营商转变 在VHDL中,移位操作符用于对数据执行位操作,方法是将其第一个操作数的位向右或向左移动和旋转。 VHDL支持以下杂项操作符:

注意:运算符按其优先级计算。(即从高到低)

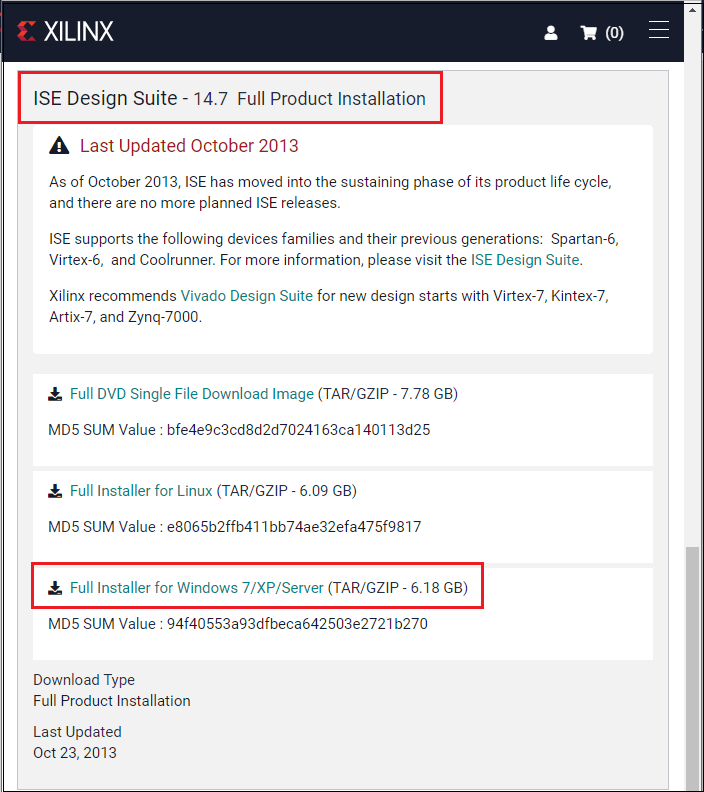

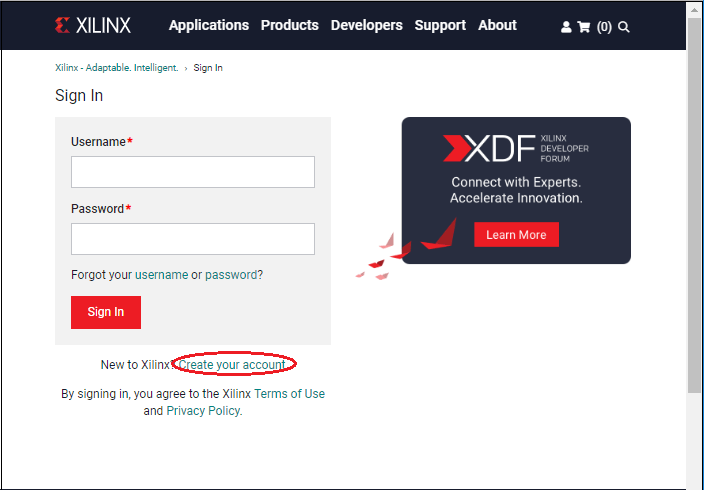

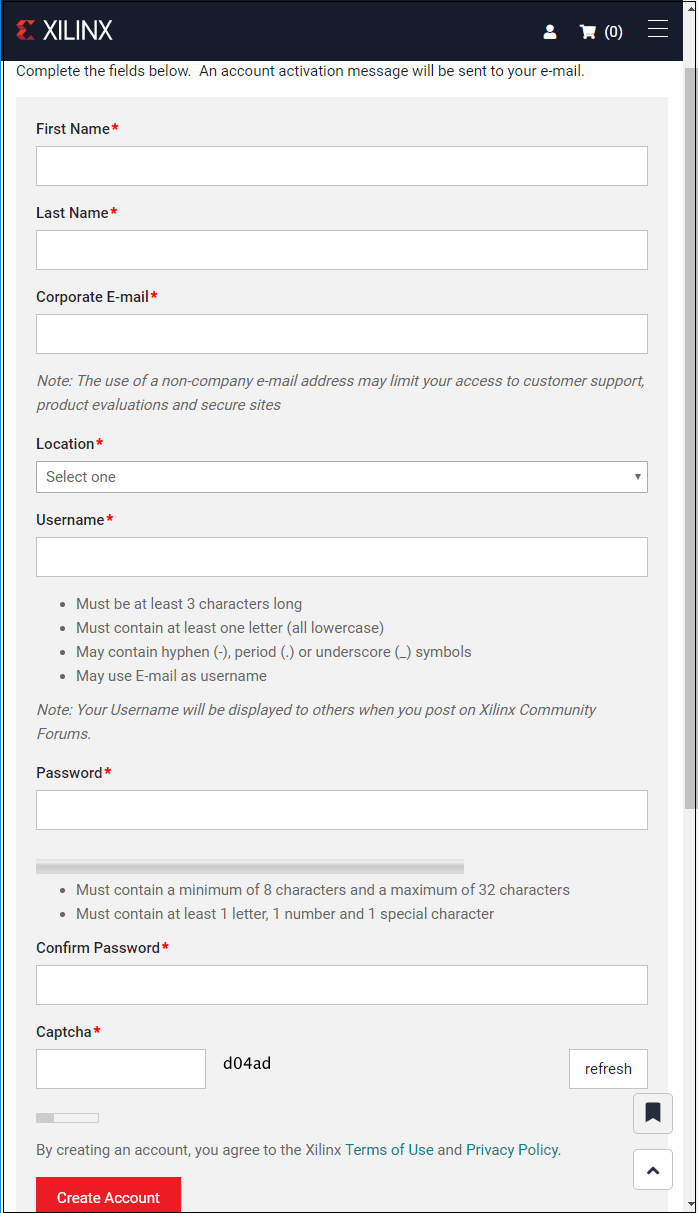

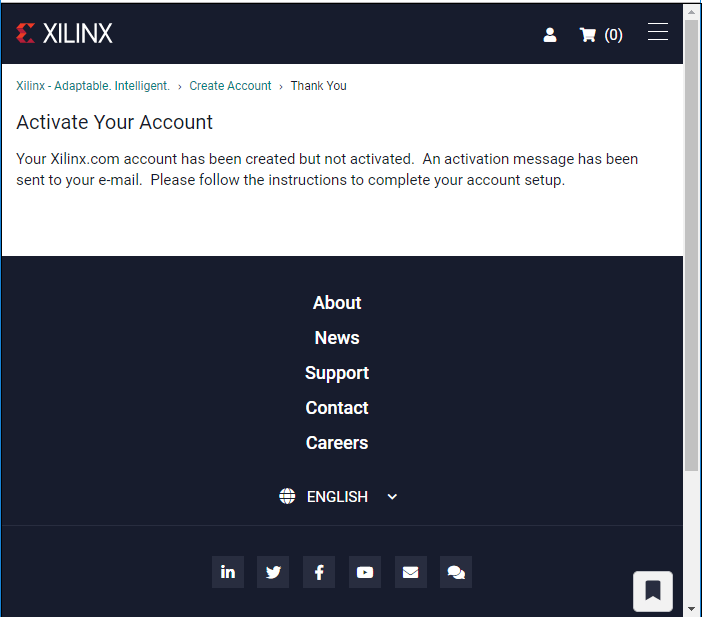

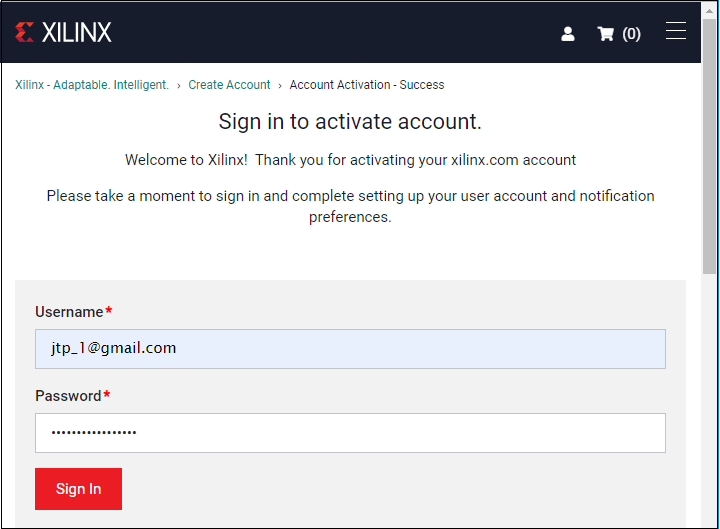

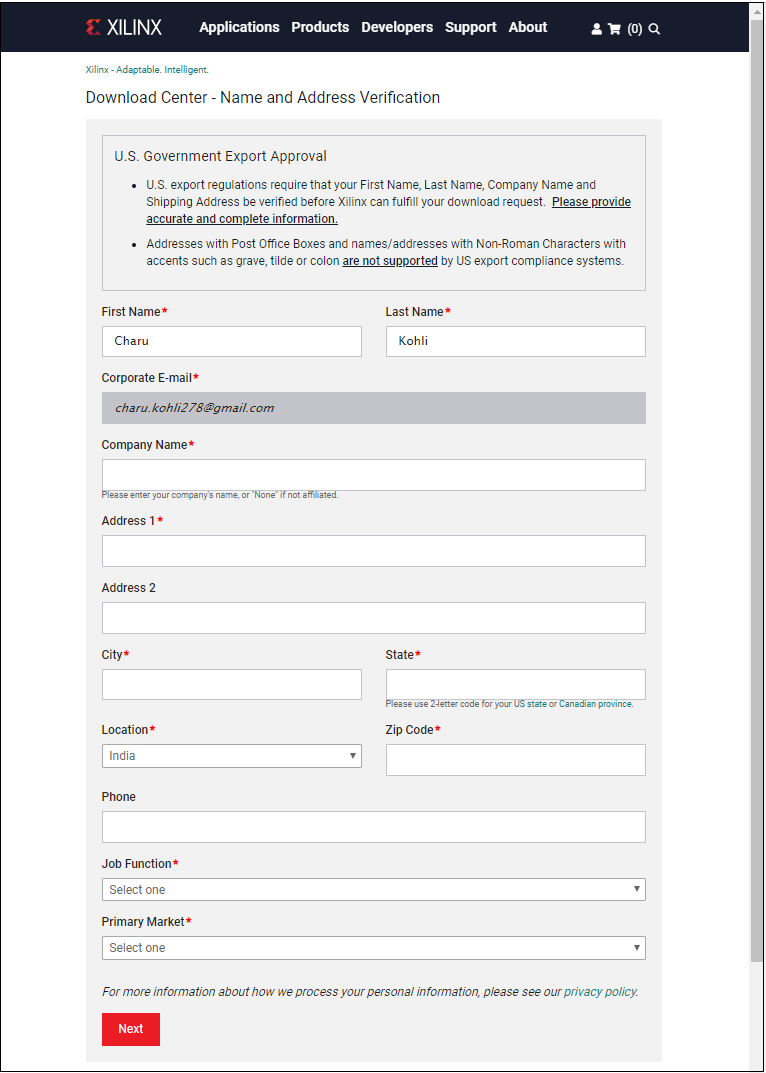

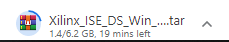

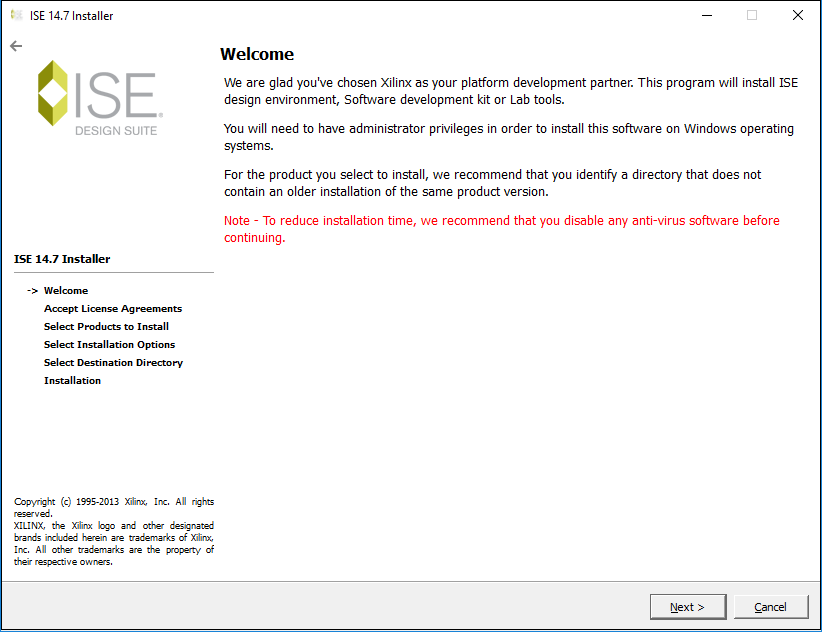

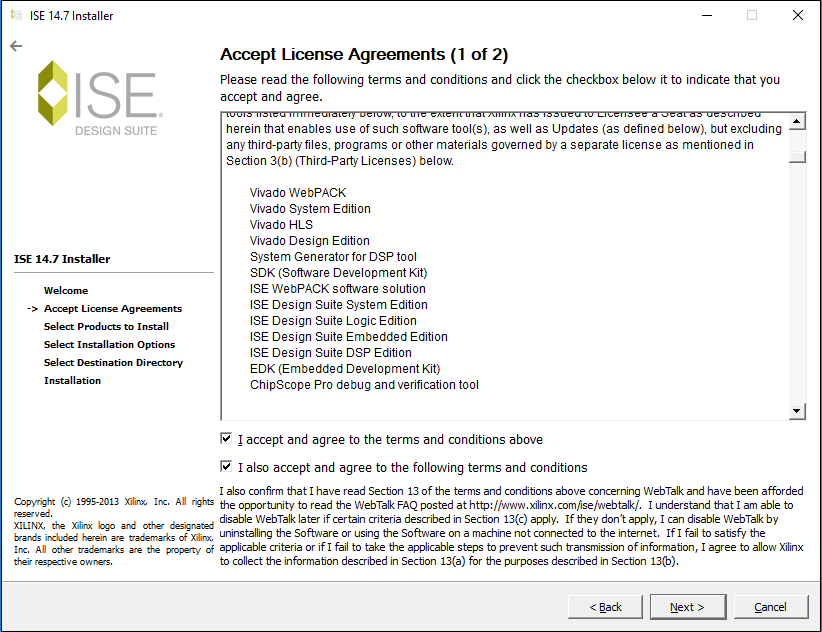

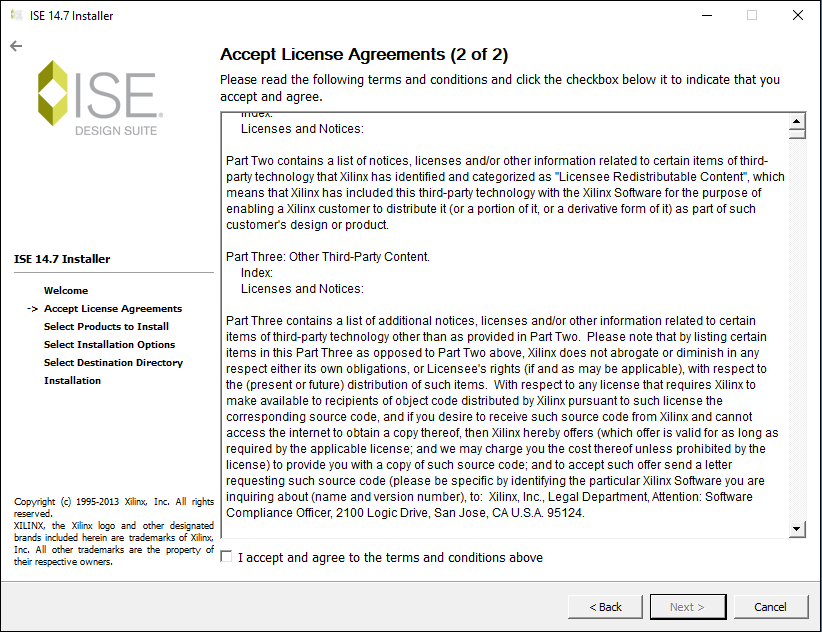

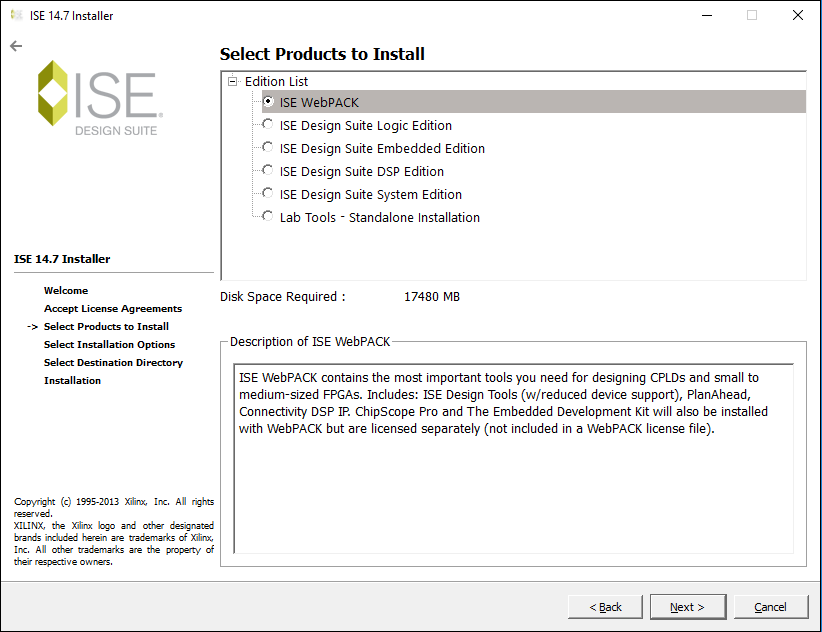

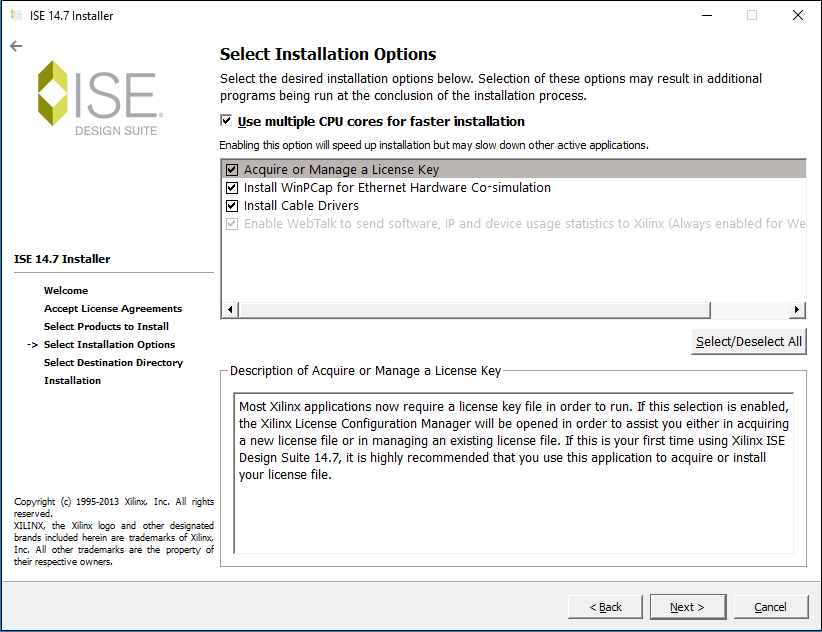

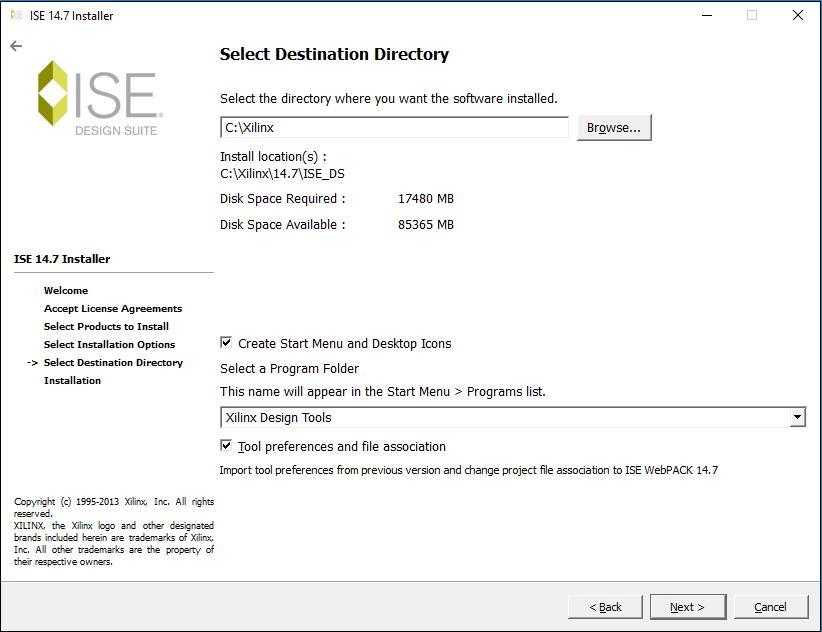

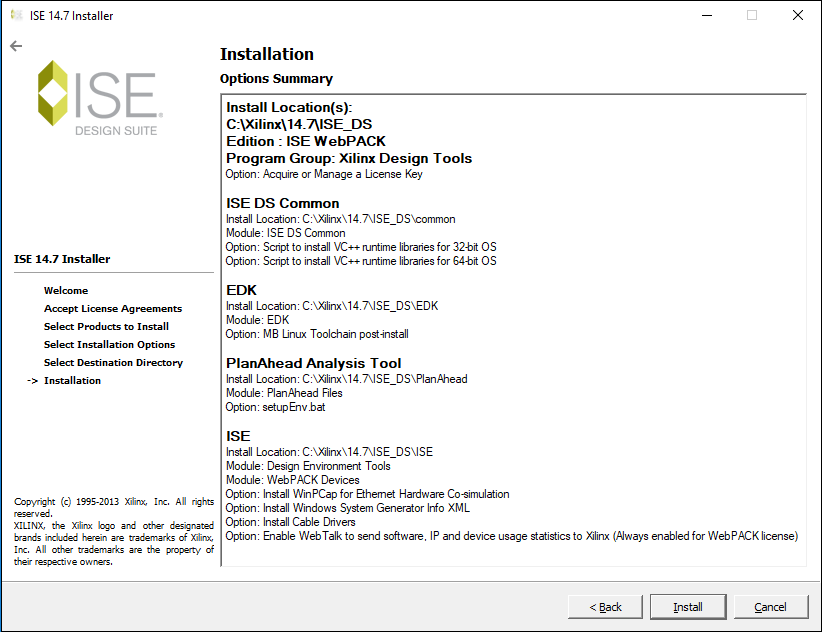

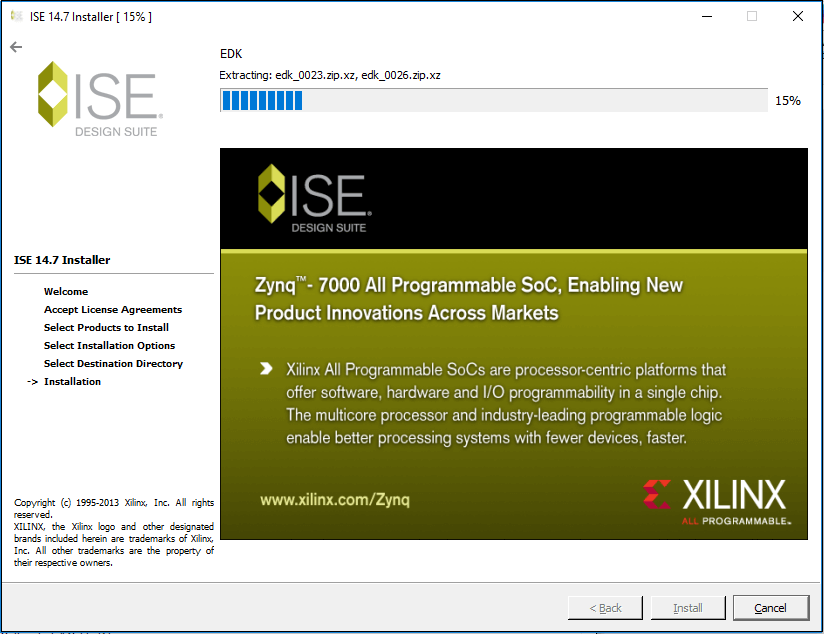

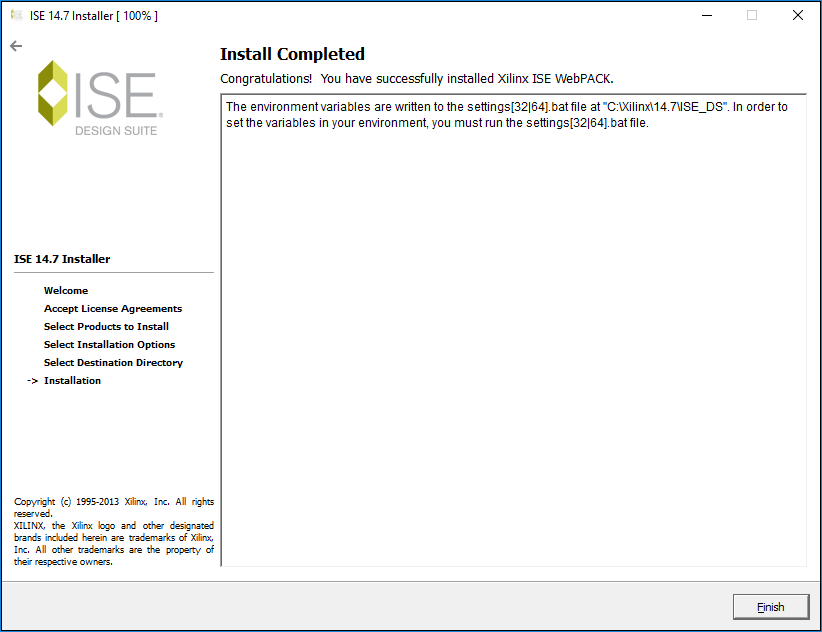

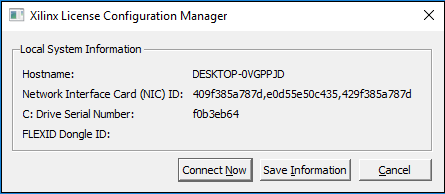

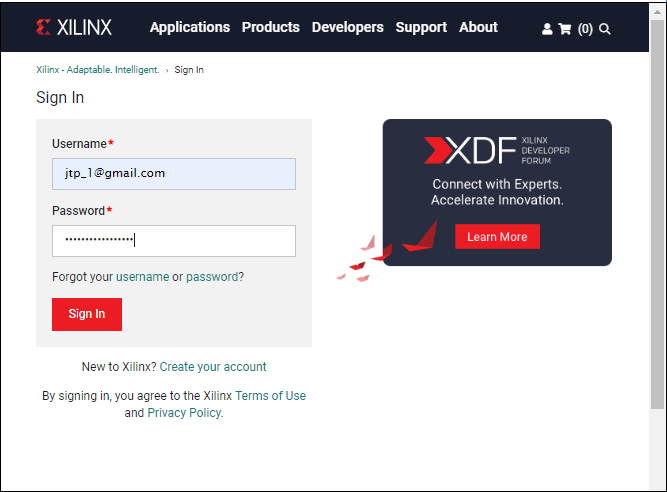

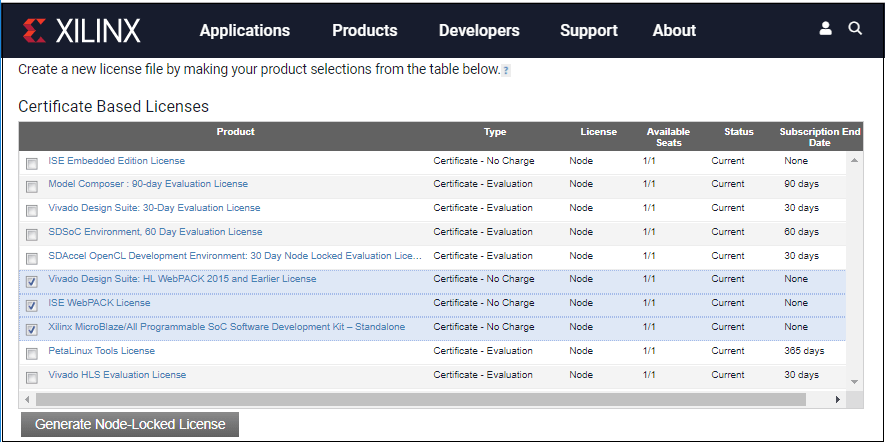

优先级相等的运算符从左到右求值。 安装Xilinx ISE工具安装Xilinx ISE Tool -的操作步骤如下 步骤1:点击下面的链接下载Xilinx ISE工具。 步骤2:现在转到ISE设计套件- 14.7完整的产品安装并选择Windows 7/XP服务器的完整安装程序(TAR/GRIP - 6.18 GB)如下图截图所示。  步骤3:一旦你点击“windows 7/XP/Server的完整安装程序,你会看到一个Xilinx标志在页面中出现。如果您没有Xilinx的帐户,请单击创建您的帐户.  步骤4:在注册页面填写信息,然后点击创建账户.  步骤5:在点击创建账户,显示如下窗口。  步骤6:现在,您将在已注册的电子邮件id上收到一封包含激活链接的邮件。点击链接激活您的帐户。 第七步:一旦你点击链接,a登录激活帐户窗口出现在窗口中,在其中输入您的用户名而且密码,然后点击登录.  第八步:现在点击下面的链接的名字而且地址验证。 https://www.xilinx.com/member/forms/download/xef.html?filename=Xilinx_ISE_DS_Win_14.7_1015_1.tar 步骤9:填妥验证表单,按下一个.  第十步:现在,你可以看到Xilinx_ISE焦油文件开始下载。  步骤11:双击下载的文件并解压该文件以运行xsetup.exe。 步骤12:运行应用程序后,执行以下操作欢迎窗口出现在屏幕上。  步骤13:在本人接受及同意上述条款及细则在上面打勾本人亦接受及同意以下条款及条件然后点击Next。   步骤14:现在,选择列出的要安装的产品。对于VHDL,选择伊势WebPACK,这是该软件的免费版本。选择ISE WebPACK后,单击下一个.  步骤十五:出现“安装选项”窗口。在此窗口中,单击下一个.  步骤16:选择目标目录,然后点击下一个.  步骤17:你可以看到安装总结在下面的截图中。点击安装来安装赛灵思  步骤18:您可以看到安装正在进行中。  步骤19:安装完成后,单击完成.  步骤20:修复项目导航器、iMPACT和许可证管理器 修复项目导航器、iMPACT和许可证管理器的步骤如下。

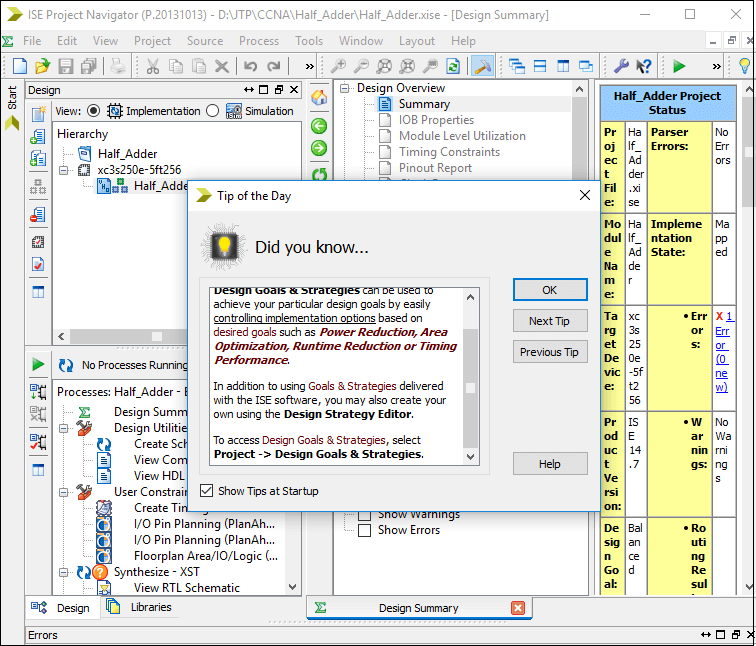

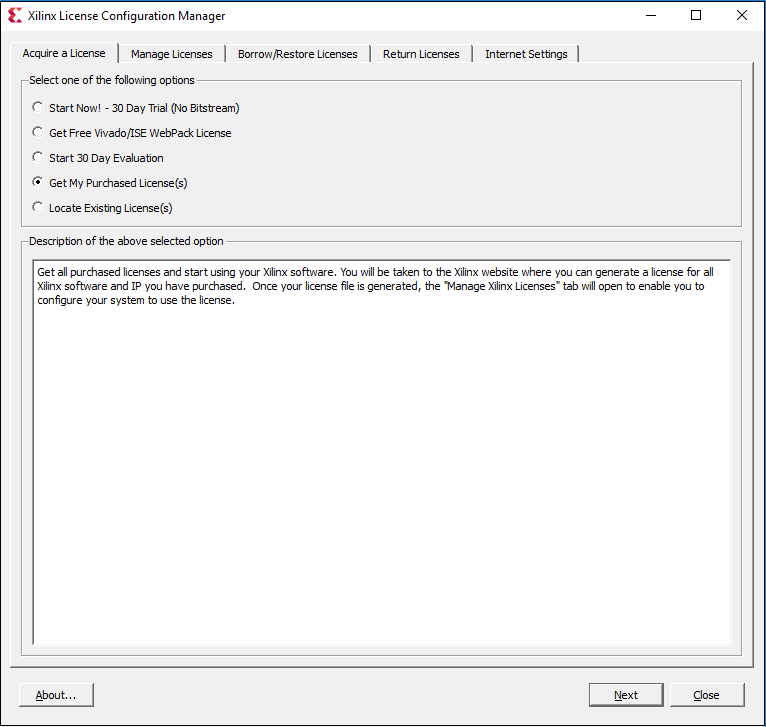

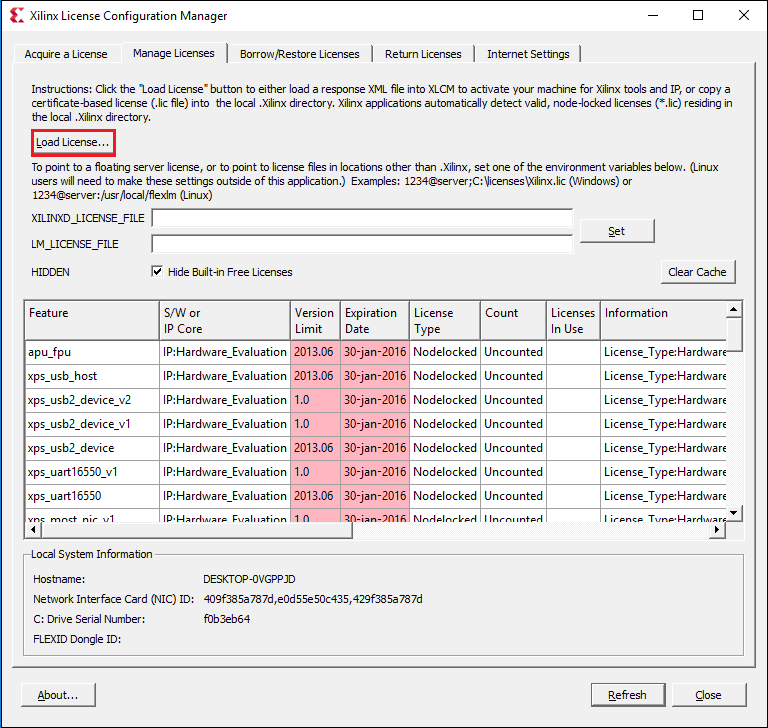

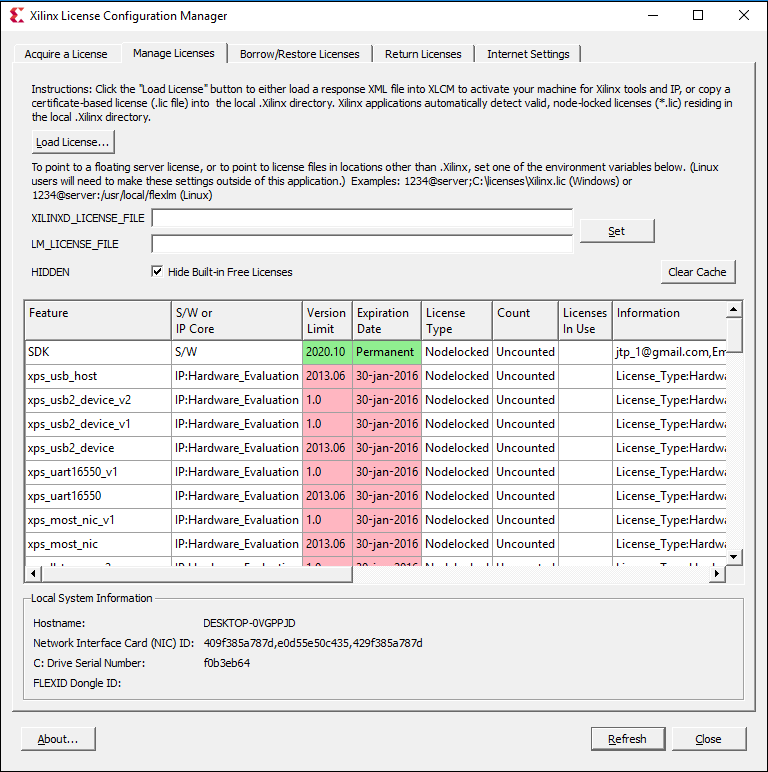

完成上述步骤后,可以关闭该目录。 步骤21:现在,您可以看到IDE Design Suite出现在屏幕上。双击IDE Design Suite,可以看到弹出如下:  22步:现在,出现以下窗口,弹出窗口,单击弹出窗口中的OK。  23步:当您单击许可证时,将打开以下窗口,其中选择领取我已购买的牌照然后点击下一个.  24步:要连接到默认浏览器,请单击现在连接.  25步:它会打开一个新的XILINX页面在浏览中。在此页上,输入用户名而且密码然后点击登录.  26步:单击Sign In后,将出现以下窗口。  27步:选择文件后,将在您注册的电子邮件id中收到一封电子邮件,该电子邮件id由Xilinx.lic文件。您需要下载这个文件。 点击加载许可证上传下载的许可证文件,然后点击关闭。  28步:文件上传后,弹出消息安装牌照成功,点击弹出的确定,然后点击关闭。 下面的截图显示许可证已经上传。  29步:现在,您可以在Xilinx工具中创建项目。

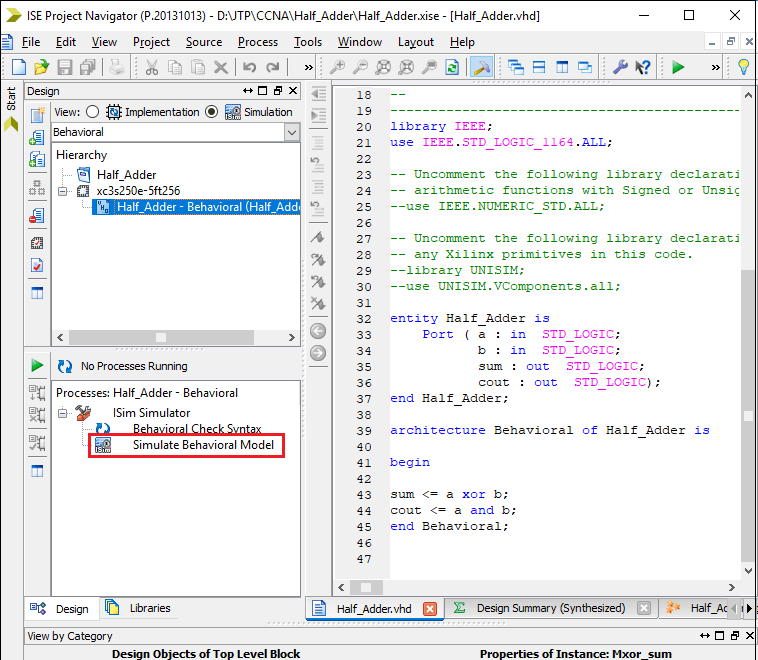

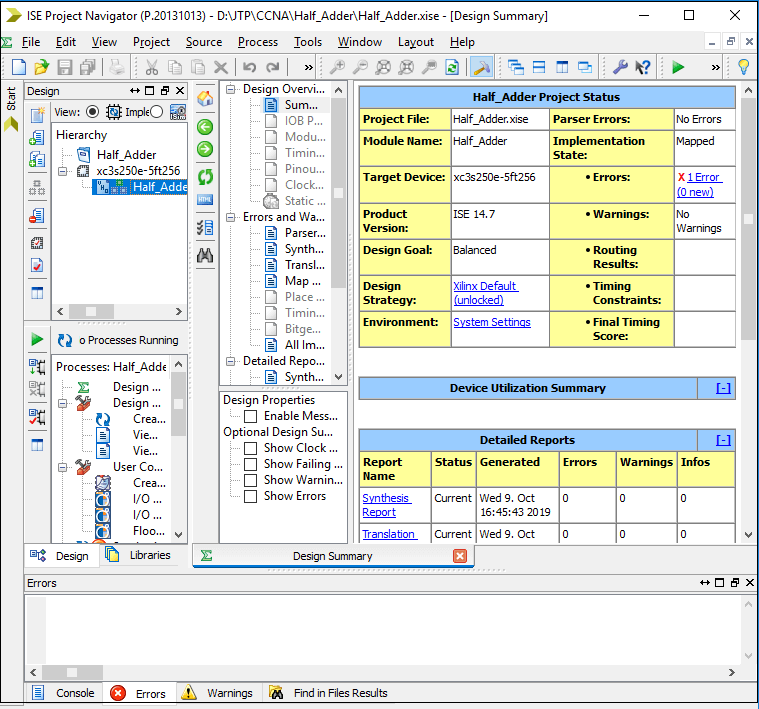

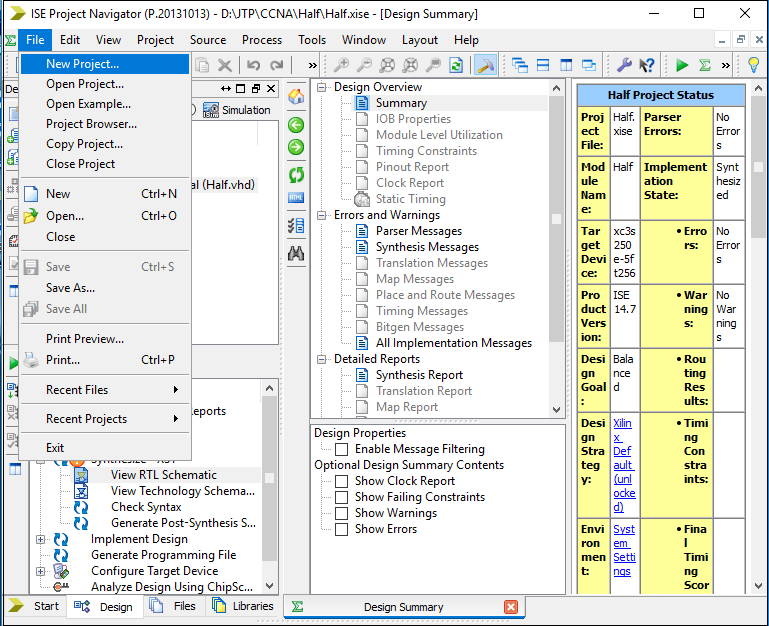

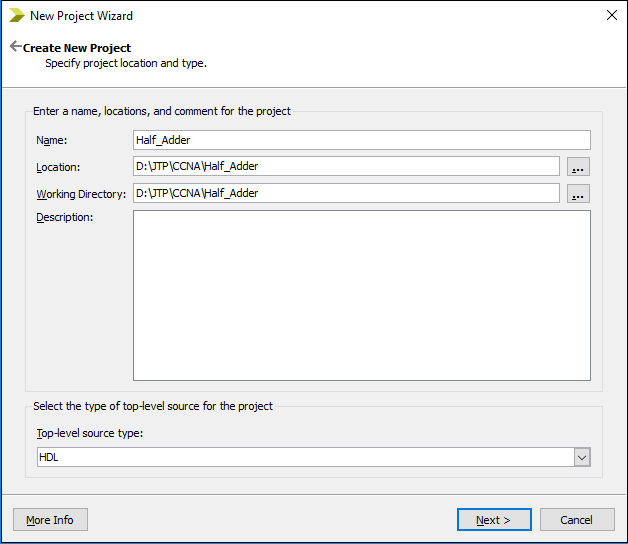

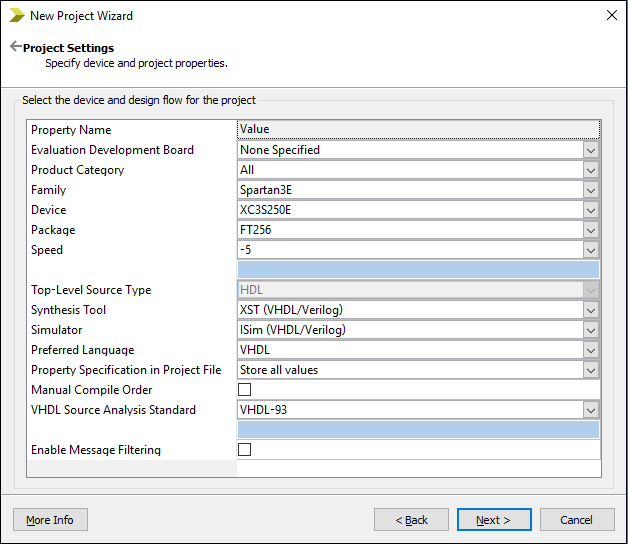

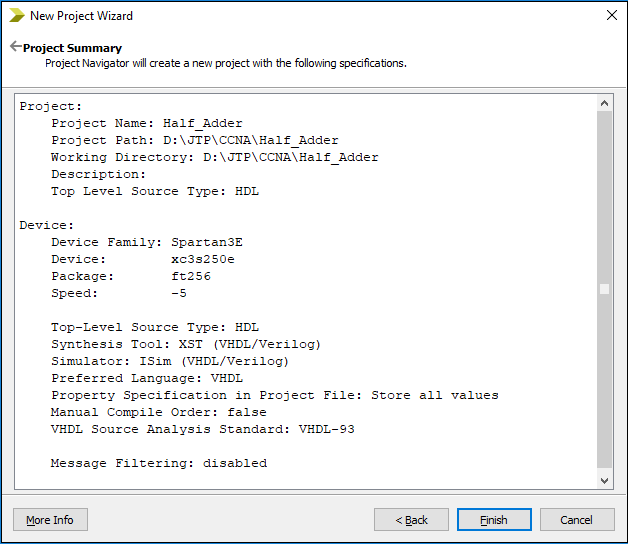

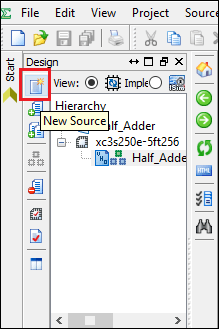

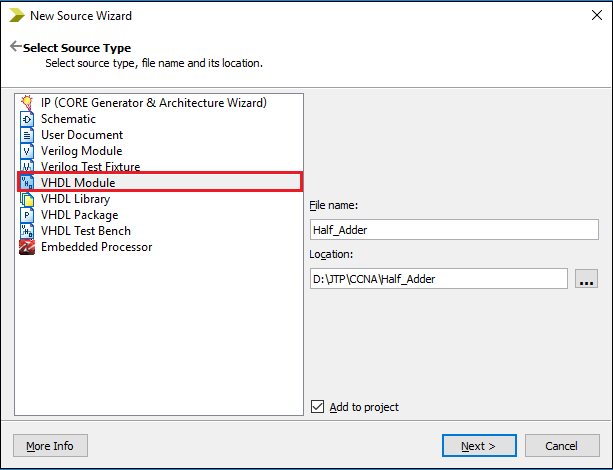

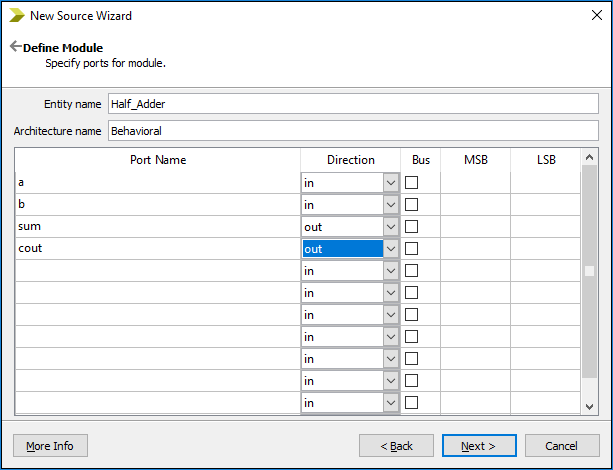

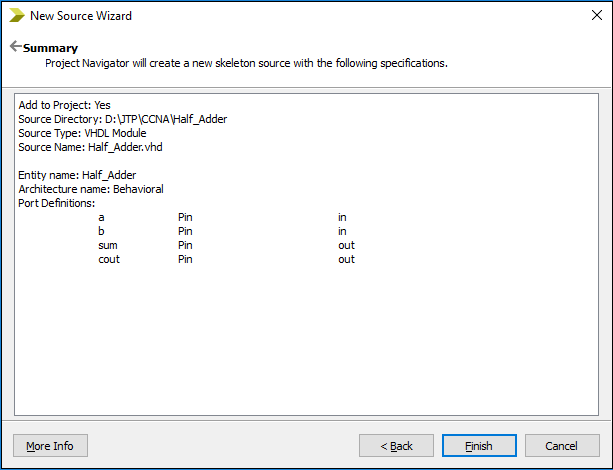

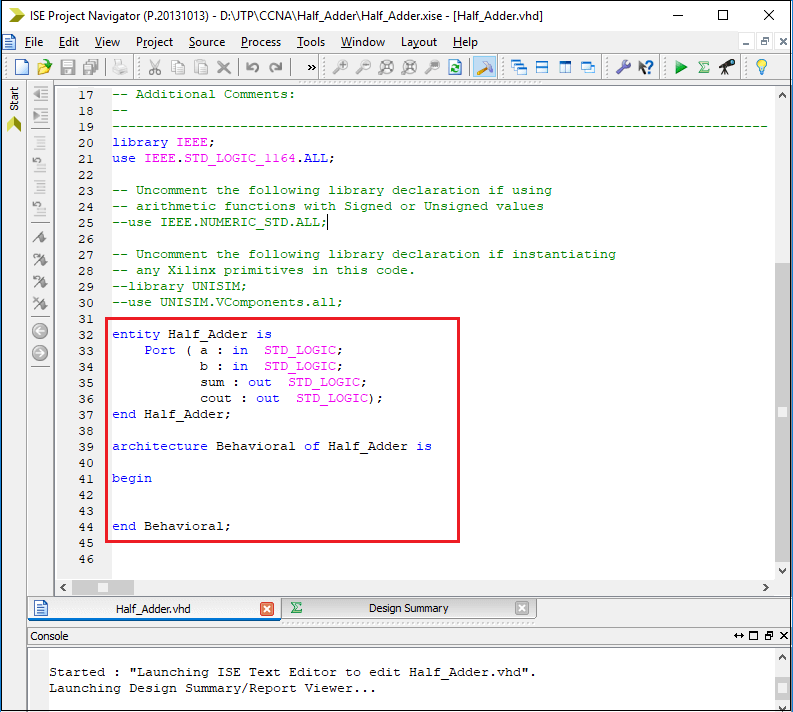

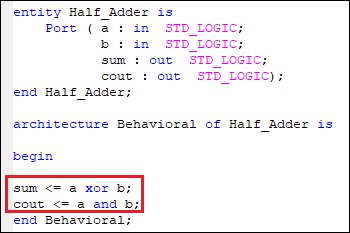

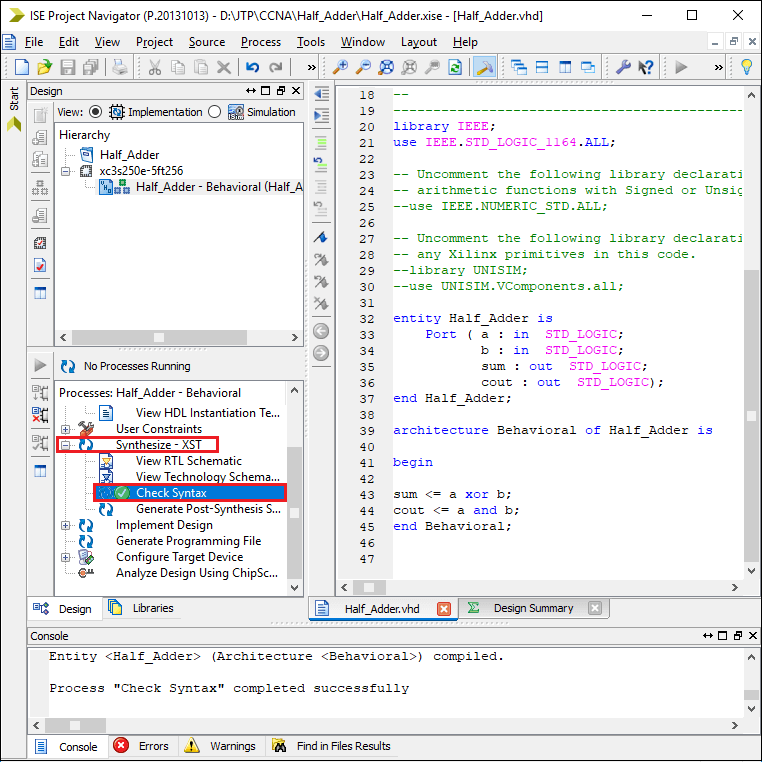

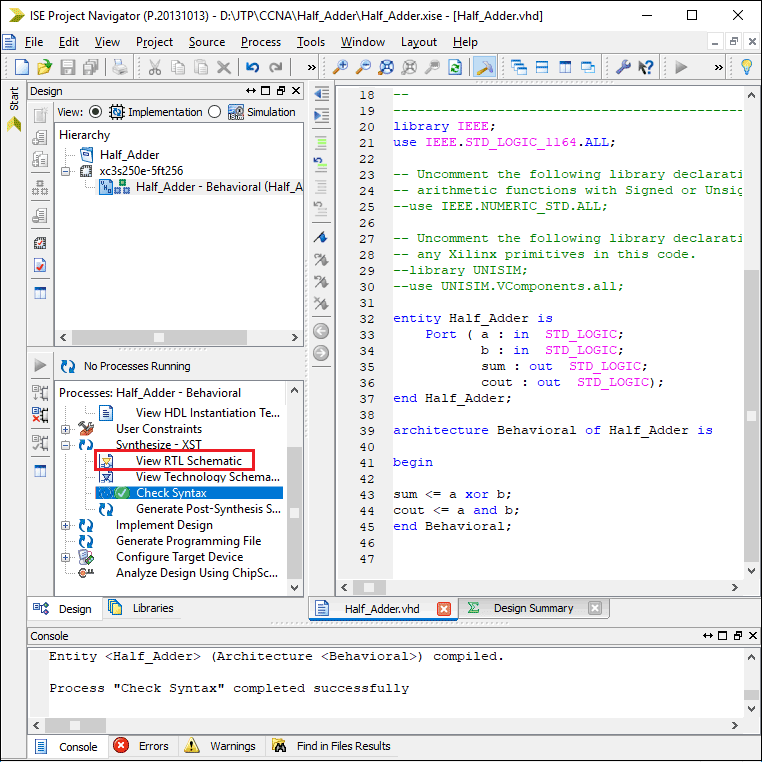

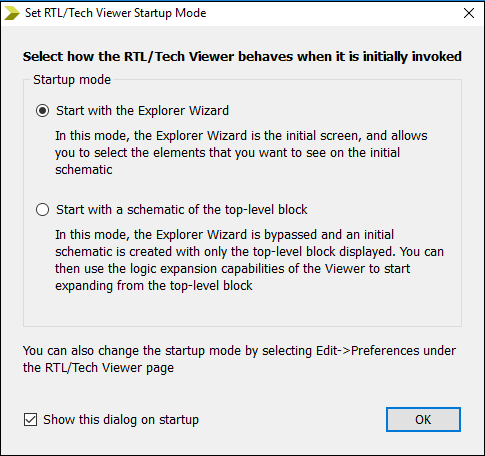

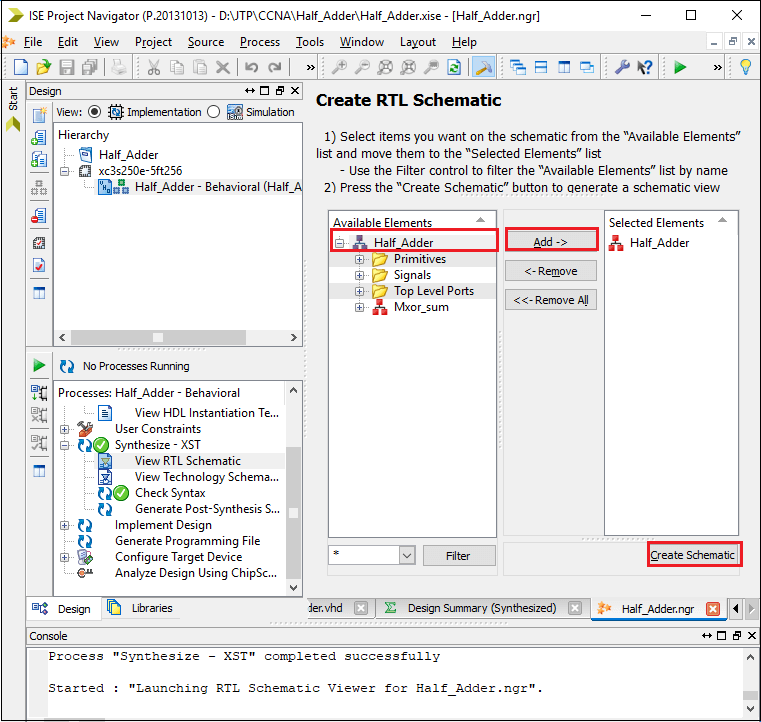

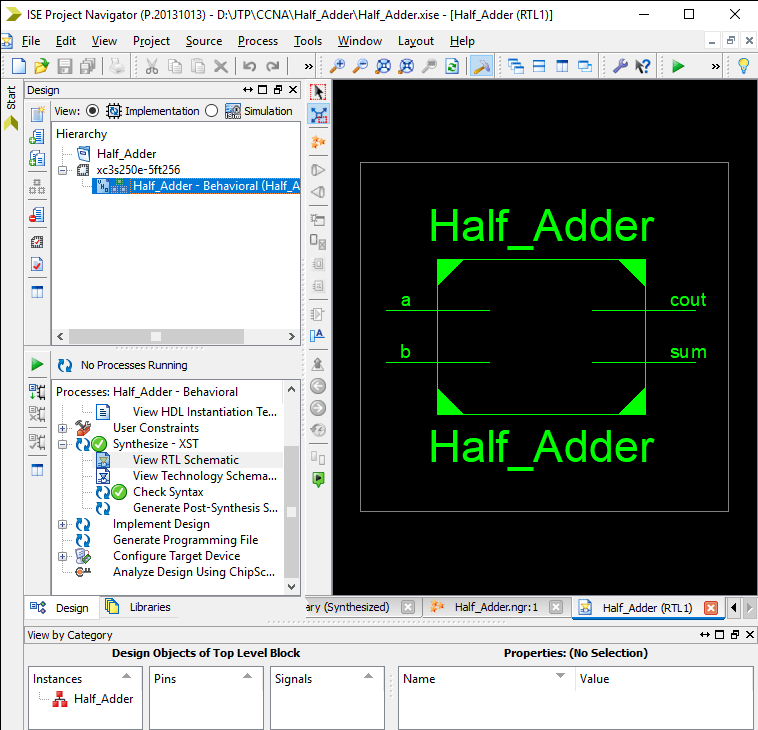

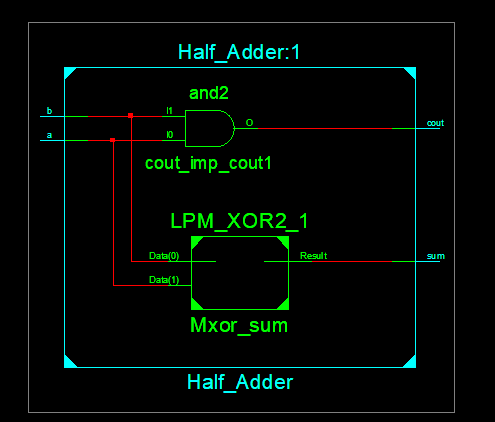

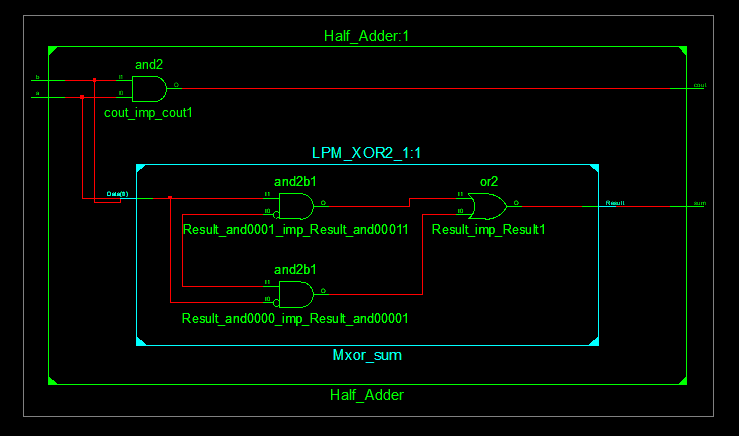

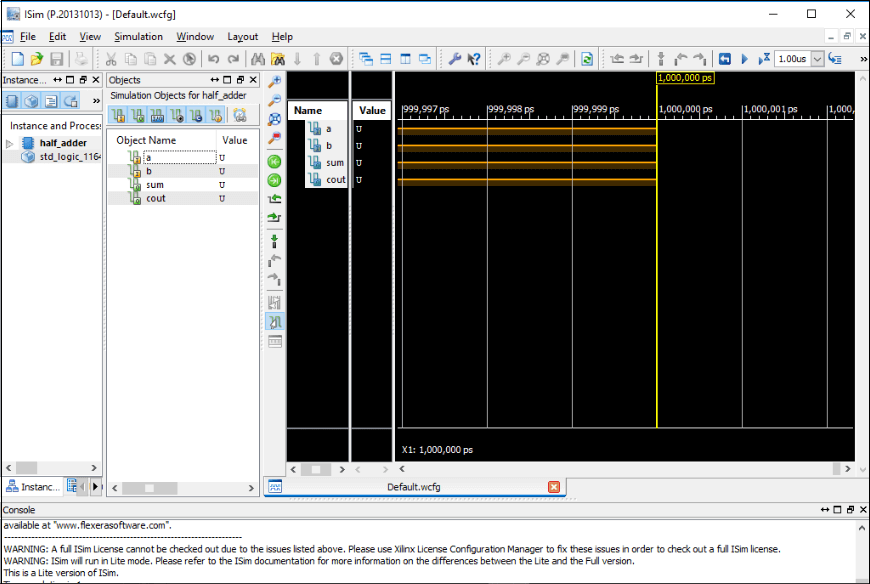

使用Xilinx IDE工具在VHDL中创建一个项目在Xilinx -中创建项目的步骤如下 步骤1:创建一个新项目 要创建新项目,请选择File ->新建项目.它将在桌面上打开一个新的项目窗口。  在新项目窗口中,给出项目名称你想要创造的指定位置(目录路径)您想要保存项目的位置,然后单击下一个.  注意:确保选择的顶级源类型是HDL,而不是Schematic、EDIF或其他东西。在点击下一个按钮,将出现以下窗口,其中显示项目属性。根据您的要求填写属性,然后单击下一个.  在点击下一个按钮时,将出现以下窗口,其中显示项目总结.如果项目摘要符合您的要求,则单击完成.否则,单击回来并按您的要求填写财产。  步骤2:创建VHDL源 要在VHDL中添加VHDL源,单击新源,或单击项目向导中的项目->新来源.  键入文件名,指定位置,然后选择硬件描述语言(VHDL)模块作为源类型。确保添加到项目复选框,然后单击下一个.  步骤3:为VHDL源分配端口 要设计半加法器,您可以指定一个端口名称作为A b求和,而且cout.在一个而且b被视为输入端口,因此从下拉菜单中选择in。总和而且cout被视为输出端口,所以选择出从下拉菜单中。  下面的截图显示了项目的摘要。  步骤4:输入并编辑VHDL代码 下面的截图显示了自动生成的Half_Adder代码。  要设计Half_Adder,在工作区域输入以下代码。  第五步:合成代码 完成源文件后,需要检查设计的语法。要检查语法,单击synthesis - xst流程以展开层次结构。现在,双击检查语法. 您可以看到ISE编译进程已经启动。如果ISE进程成功完成,将出现一个绿色复选标记。否则,将出现一个红色的X,这表明存在错误和流程失败。  要查看半加法器的基本设计,双击查看RTL原理图.  现在,您将看到以下弹出窗口,其中单击好吧.  在创建RTL Schematic中,从可用的列表,然后点击添加按钮,将所选项目移动到选中的元素然后点击创建原理图.  现在,你可以在屏幕上看到半个Adder的外部设计。  当您双击上面的矩形时,您可以看到使用逻辑门的内部图。   步骤6:模拟行为模型(ISE模拟器) 要检查行为模型,选择Implementation-> Half_Adder- behavioral (Half_Adder.vhd)并双击模拟行为模型。

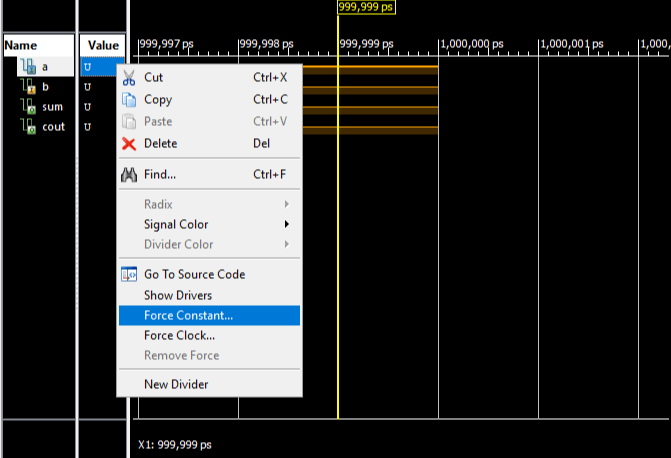

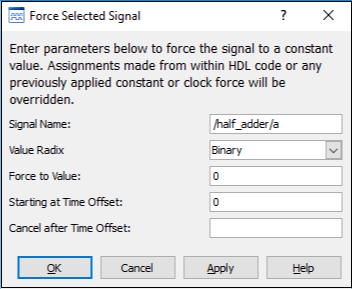

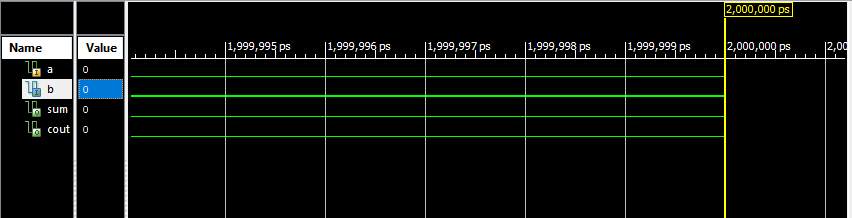

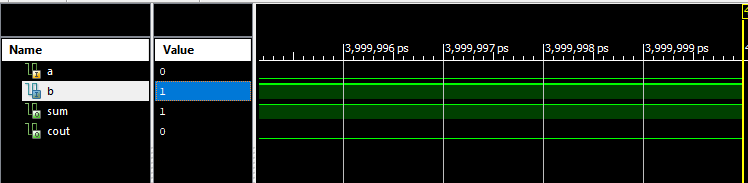

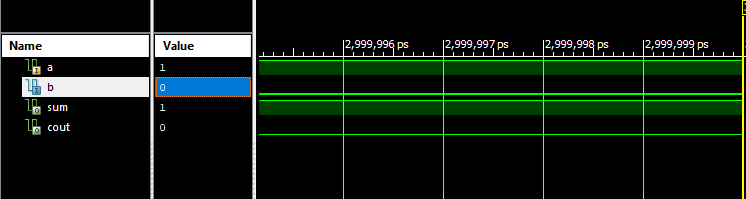

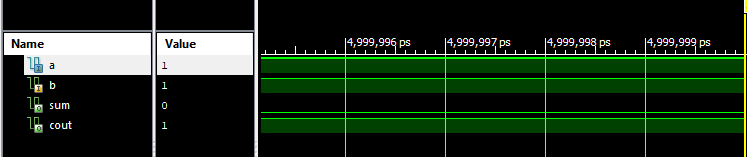

如果模拟成功,将打开以下窗口。  要分配值,右键单击给定的值(U),然后选择力常数。考虑下面的图像:  将出现以下弹出窗口,您可以在其中分配a的值,然后单击Apply和OK。  案例1:如果输入为: A = 0 输出: Sum = 0  例2:如果输入是- A = 0 输出: Sum = 1  案例3:输入是- A = 1 输出: Sum = 1  案例4:输入是- A = 1 输出: Sum = 0

VHDL vs. C语言

先决条件在学习VHDL之前,您必须具备电子电路的基本知识。 观众我们的VHDL教程旨在帮助初学者和专业人士。 问题我们向您保证,在本VHDL教程中不会发现任何问题。但如果有任何错误或错误,请将错误贴在联系表格上。 |

观看视频请加入我们的Youtube频道:现在加入

观看视频请加入我们的Youtube频道:现在加入

反馈

- 将你的反馈发送至(电子邮件保护)

帮助他人,请分享